专用集成电路CMOS组合逻辑设计 集成电路设计的核心基石

在当今信息技术的浪潮中,专用集成电路(ASIC)扮演着至关重要的角色,它为实现特定功能提供了高效、定制化的硬件解决方案。而在ASIC设计的广阔领域中,基于CMOS(互补金属氧化物半导体)工艺的组合逻辑设计,构成了其最基础、最核心的数字电路设计模块。本文旨在探讨专用集成电路中CMOS组合逻辑设计的关键概念、设计流程及其在现代集成电路设计中的重要性。

CMOS技术与组合逻辑

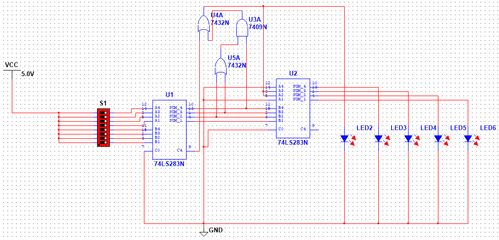

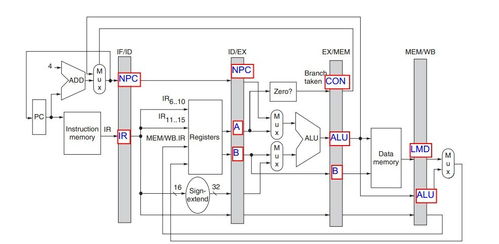

CMOS技术因其极低的静态功耗、高噪声容限以及与纳米级制造工艺的良好兼容性,已成为现代数字集成电路的绝对主流。组合逻辑电路,顾名思义,其输出仅取决于当前的输入信号组合,不包含任何存储元件(如触发器),因此不具有记忆功能。常见的组合逻辑电路包括与门、或门、非门、与非门、或非门、异或门、多路复用器、译码器和编码器等。这些基本门电路是构建更复杂数字系统(如算术逻辑单元、控制单元)的“砖石”。

CMOS组合逻辑设计的基本原理

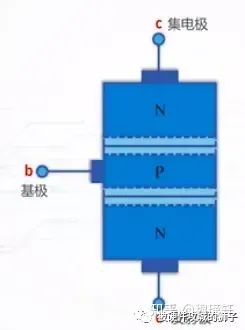

CMOS组合逻辑门的设计,本质上是利用PMOS晶体管和NMOS晶体管的互补特性来构建逻辑功能。基本设计原则可概括为:

1. 下拉网络(PDN):由NMOS晶体管构成,负责实现逻辑函数的“真”值部分(即输出为逻辑0的条件)。当输入满足特定组合时,PDN导通,将输出节点拉低至地电平(逻辑0)。

2. 上拉网络(PUN):由PMOS晶体管构成,负责实现逻辑函数的“假”值部分(即输出为逻辑1的条件)。当输入不满足PDN导通条件时,PUN导通,将输出节点拉高至电源电压(逻辑1)。

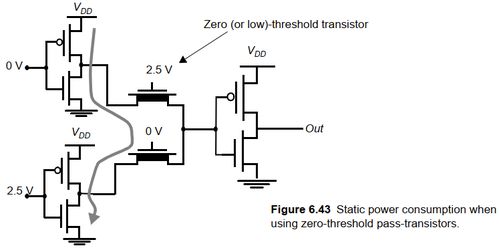

PUN和PDN在电气特性上互为对偶,确保在任何静态输入组合下,两条通路不会同时导通,从而实现了极低的静态功耗。

设计流程与考量因素

一个稳健的CMOS组合逻辑设计流程通常包括以下步骤:

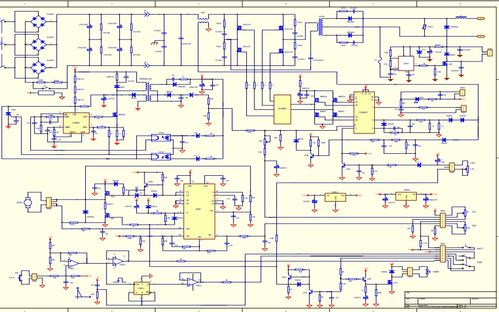

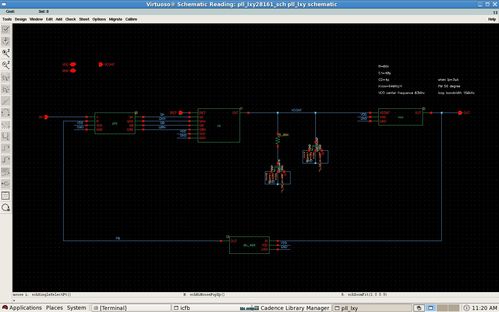

- 逻辑功能定义与优化:首先使用硬件描述语言(如Verilog或VHDL)或逻辑图明确定义所需功能,并利用卡诺图或逻辑综合工具进行布尔逻辑优化,以最小化门级复杂度。

- 电路结构选择:根据性能、面积和功耗要求,选择合适的电路结构。例如,静态CMOS逻辑是最可靠、最常用的结构;而动态CMOS逻辑、传输门逻辑等则在特定场景(如高性能、高密度)下有其优势。

- 晶体管尺寸确定(尺寸标注):这是设计的关键环节。需要根据驱动能力、负载电容、上升/下降时间(时序要求)和功耗约束,精心计算每个晶体管的宽长比(W/L)。通常使用模拟电路仿真工具(如SPICE)进行反复迭代验证。

- 版图设计与验证:将电路图转换为符合特定CMOS工艺设计规则的物理掩膜版图。这需要考虑晶体管布局、布线、寄生参数(电阻、电容)、信号完整性、电源网络和可靠性(如天线效应、闩锁效应)等诸多因素。版图后提取参数并再次进行仿真验证至关重要。

- 时序与功耗分析:在设计的各个阶段,都需要对电路的传播延迟、建立/保持时间以及动态/静态功耗进行严格分析和优化,以满足系统级指标。

面临的挑战与未来趋势

随着工艺节点不断向7纳米、5纳米甚至更小尺寸演进,CMOS组合逻辑设计面临着前所未有的挑战:

- 短沟道效应与泄漏电流:晶体管尺寸缩小导致亚阈值泄漏电流急剧增加,静态功耗管理变得异常困难。

- 工艺波动与可靠性:制造过程中的微小变异对电路性能的影响愈发显著,设计必须考虑工艺角(Process Corner)和蒙特卡洛分析以确保良率。

- 互连线延迟主导:在深亚微米工艺下,互连线(金属线)的电阻和电容导致的延迟已超过晶体管本身,成为时序性能的主要瓶颈。

为应对这些挑战,设计方法学也在不断发展,例如广泛采用标准单元库、基于时序驱动的综合与布局布线流程、以及引入多阈值电压(Multi-Vt)、电源门控(Power Gating)、近阈值计算(Near-Threshold Computing)等低功耗设计技术。

###

总而言之,CMOS组合逻辑设计是专用集成电路设计的基石。它不仅仅是简单门电路的堆砌,更是一门在性能、功耗、面积和可靠性之间寻求精妙平衡的艺术与科学。深入理解其基本原理,熟练掌握从逻辑到版图的全流程设计方法与EDA工具,是每一位集成电路设计工程师必备的核心技能。随着芯片复杂度指数级增长和“摩尔定律”的演进,CMOS组合逻辑设计将继续作为创新与突破的起点,推动着从人工智能加速器到物联网终端等各类专用芯片的飞速发展。

如若转载,请注明出处:http://www.mytouchtime.com/product/60.html

更新时间:2026-04-16 17:42:47